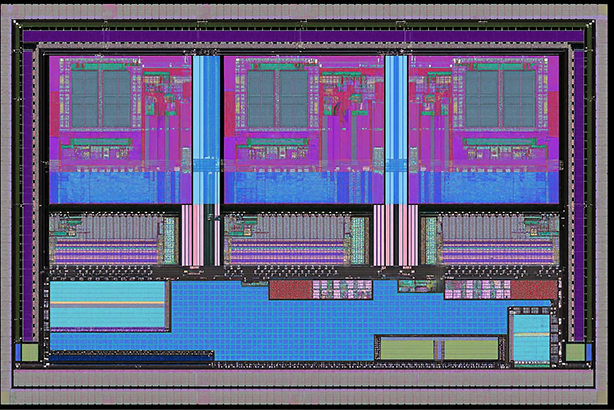

SoC/ASIC Design & Verification

At Seminovaa™, we design and verify high-performance ASICs and complex SoCs tailored to your specific application needs. Our engineering teams bring deep domain expertise across the entire chip development cycle — from RTL design, IP integration, and low-power architecture to functional verification using industry-standard methodologies like UVM.

Our Expertise Covers

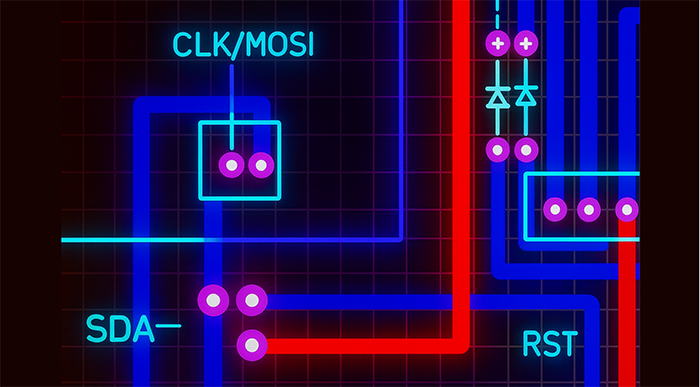

- TL design & IP integration

- Low-power architecture & multi-voltage design

- Testbench creation (C, SystemVerilog, UVM)

- Protocol verification (PCIe, DDR, Ethernet, AMBA)

- Debugging with waveform, logs, TARMAC, and co-simulation

Ensuring First-Pass Silicon Success

We employ a rigorous verification strategy — including simulation, formal verification, and emulation — to identify and address design issues early, reducing risk and accelerating time-to-market

AI-Enhanced Verification

To maximize efficiency and coverage, Seminovaa integrates Gen-AI/Agentic-AI into its DV workflows:

The Result: Comprehensive verification coverage, reduced debug cycles, and a higher probability of on-time, first-pass silicon delivery.

Enquire Now